# High Efficiency, Synchronous Buck Charger for 1-2 cell Li-ion Battery

## 1 DESCRIPTION

The SC8932A is a highly integrated switch-mode buck charger for 1-2 cell Li-ion battery applications. It supports up to 13.5V input, up to 3A charging current and provides battery charge management functions including trickle charge, constant current charge, constant voltage charge, charge termination and charging status indication.

The SC8932A supports flexible charge current option, and the user can program the current freely through external resistor for different applications. With the charger management function, the IC can be used to charge 1-2 cell Li-ion battery. SC8932A charges batteries with high efficiency, 5V to 3.5V@2A 95.5%, 9V to 7V@2A 97.1%.

The SC8932A supports input current limit, input under voltage and over voltage protections, internal cycle by cycle current limit, battery short circuit protection, and output over voltage protection. It also offers charging safety timer and over temperature protection to ensure safety under different abnormal conditions. The SC8932A features I2C interface, so the user can easily set the input current limit, output current limit, switching frequency and output voltage through I2C.

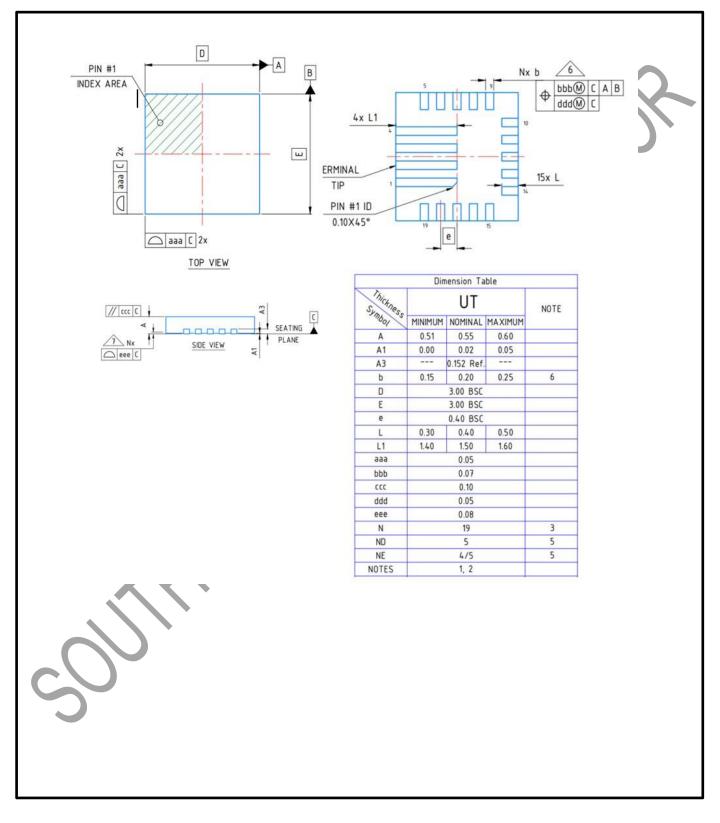

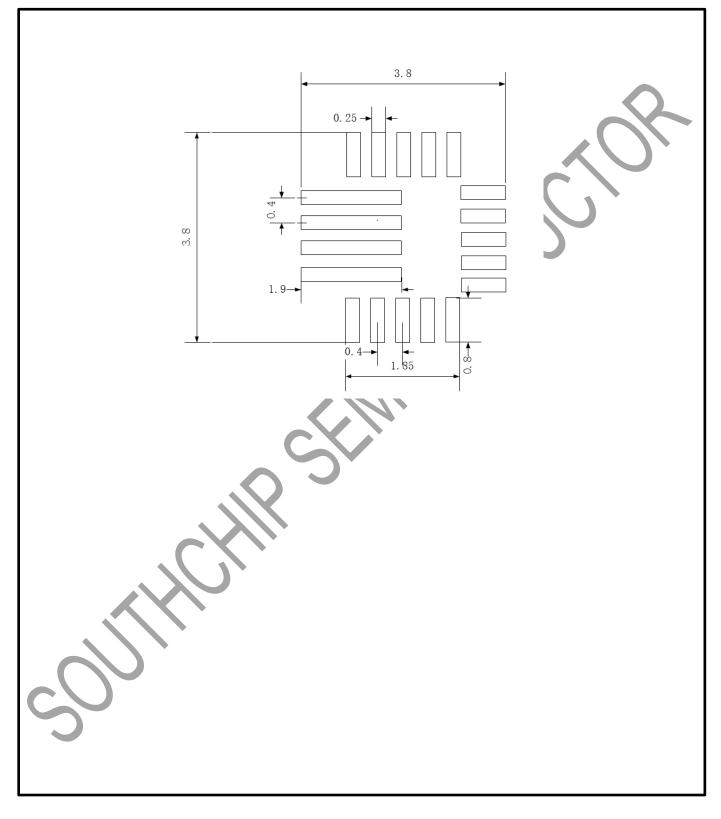

The SC8932A is available in QFN-3\*3(FC) package

#### **3 APPLICATIONS**

- Blue Tooth Speaker Charger

- Portable Media Players

- Notebook, Tablet

- POS Machine

## 2 FEATURES

- Integrated Synchronous Buck Charger

- Charging Management (Trickle Charge / Constant Current Charge / Constant Voltage Charge / Charge Termination)

- Programmable Constant Charge Current

- Selectable Target Voltage:

- 1 Cell: 4.2V/4.3V/4.35V/4.4V

- 2 Cell: 8.4V/8.6V/8.7V/8.8V

- Adjustable Safety Timer

- 600kHz Switching Frequency

- Charge Status Indication

- NTC for Battery Protection(support JEITA standards)

- Adjustable Input Current Limit

- Input Under Voltage and Over Voltage Protection

- Battery Over Voltage Protection

- Battery Short Protection

- Thermal Regulation and Shutdown

- FCQFN 3X3 Footprint

## 4 DEVICE INFORMATION

| Part Number | Package   | Dimension          |

|-------------|-----------|--------------------|

| SC8932AQFKR | FCQFN-3*3 | 3mm X 3mm X 0.55mm |

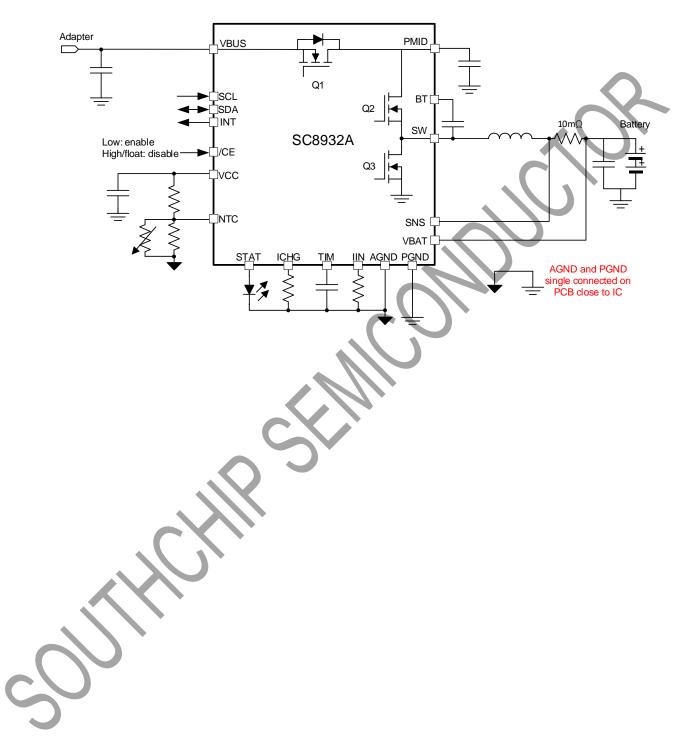

# 5 Typical Application Circuit

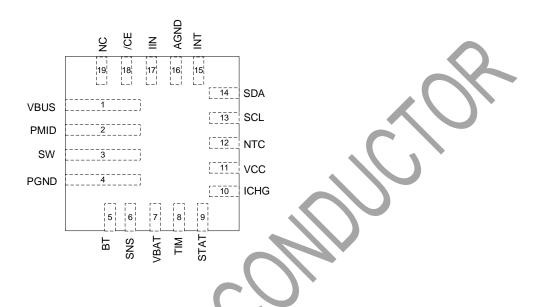

# 6 Terminal Configurations and Functions

|        | TERMINAL |     | DESCRIPTION                                                                                                                                                                                         |

|--------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER | NAME     | I/O |                                                                                                                                                                                                     |

| 1      | VBUS     | I   | Power supply pin.                                                                                                                                                                                   |

| 2      | PMID     | 0   | Input of buck charger to charge the battery cells. Connected to the drain of the reverse blocking MOSFET.                                                                                           |

| 3      | SW       | Ю   | Switching node of the buck converter. Connect to external inductor.                                                                                                                                 |

| 4      | PGND     | Ю   | Power ground.                                                                                                                                                                                       |

| 5      | BT       | 10  | Bootstrap pin. Connect a 100nF ceramic capacitor between BT pin and SW pin to provide bias voltage for internal driver circuit.                                                                     |

| 6      | SNS      | 1/0 | Charge current positive sense pin.                                                                                                                                                                  |

| 7      | VBAT     | 1/0 | Charge current and battery voltage sense pin                                                                                                                                                        |

| 8      | ТІМ      | 10  | Connect a 100nF capacitor to GND to set the safety timer.                                                                                                                                           |

| 9      | STAT     |     | Charge status indication.                                                                                                                                                                           |

| 10     | ICHG     | -   | Connect a $5k\Omega$ resistor to set charge current.                                                                                                                                                |

| 11     | VCC      | I/O | Internal LDO output. Connect a 1uF capacitor with it.                                                                                                                                               |

| 12     | NTC      | I   | Connect to the Negative Temperature Coefficient (NTC) thermistor inside the battery cells to sense the battery cells temperature for protection. Short this pin to ground to disable this function. |

| 13     | SCL      | I   | I2C interface clock. Connect SCL to the logic rail through a pull up resistor (typical 10 $k\Omega$ ).                                                                                              |

| 14     | SDA      | I/O | I2C interface data. Connect SDA to the logic rail through a pull up resistor (typical 10 $k\Omega$ ).                                                                                               |

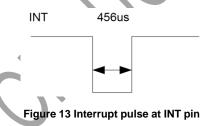

| 15     | INT      | 0   | An open drain output for interrupt signal. The IC sends a logic low pulse at INT pin to inform the host if an interrupt event happens.                                                              |

| 16     | AGND     | IO  | Analog ground. Connect with power PGND close to IC.                                                                                                                                                 |

| 17     | IIN      | I   | Connect a $5k\Omega$ resistor to set input current limit.                                                                                                                                           |

| 18     | /CE      | I   | IC enable pin. low enables IC, high or float disable IC.                                                                                                                                            |

| 19     | NC       |     | To be floating                                                                                                                                                                                      |

# 7 Specification

## 7.1 Absolute Maximum Rating

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                        |                                          | Min. | Max. | Unit |

|------------------------|------------------------------------------|------|------|------|

|                        | VBUS, PMID,                              | -0.3 | 20   | V    |

|                        | вт                                       | -0.3 | 21.5 | V    |

| Voltage <sup>(2)</sup> | VBAT, SNS, SW, /CE                       | -0.3 | 15   | V    |

| Vollage                | VCC                                      | -0.3 | 6.5  | V    |

|                        | BT-SW                                    | -0.3 | 6.5  | V    |

|                        | SNS-VBAT                                 | -0.1 | 0.1  | V    |

|                        | TIM, NTC, ICHG, IIN, STAT, INT, SCL, SDA | -0.3 | 5.5  | V    |

| TJ                     | Operating junction temperature           | -40  | 150  | °C   |

| T <sub>stg</sub>       | Storage temperature                      | -65  | 150  | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.

- (2) All voltages are with respect to network ground terminal.

- (3) VBUS, PMID, BTST, SW should be tied together to test the SW abs voltage.

#### 7.2 Thermal Information

| THERMAL RESISTA | NCE <sup>(1)</sup>                     | QFN (3mmX3mm) | Unit |

|-----------------|----------------------------------------|---------------|------|

| θ <sub>JA</sub> | Junction to ambient thermal resistance | 48            | °C/W |

| θ <sub>JC</sub> | Junction to case resistance            | 9             | °C/W |

(1) Measured on JESD51-7, 4-layer PCB.

## 7.3 ESD Ratings

|                                 |                                |          | Min. | Max. | Unit |

|---------------------------------|--------------------------------|----------|------|------|------|

| N/ (1)                          | Human-body Model (HBM) (2)     | All pins | -2   | +2   | kV   |

| V <sub>ESD</sub> <sup>(1)</sup> | Charged-device Model (CDM) (3) |          | -750 | 750  | V    |

(1) Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

(2) Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(3) Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.4 Recommended Operation Conditions

|                  |                    | MIN | TYP | МАХ  | UNIT |

|------------------|--------------------|-----|-----|------|------|

| V <sub>BUS</sub> | VBUS voltage range | 4   |     | 13.5 | V    |

| Vpmid            | PMID voltage range | 4   |     | 13.5 | V    |

SOUTHCHIP SEMICONDUCTOR

| VBAT              | VBAT voltage range             |     |     | 8.8 | V  |

|-------------------|--------------------------------|-----|-----|-----|----|

| C <sub>BUS</sub>  | Bulk capacitor for VBUS        |     | 1   |     | μF |

| C <sub>PMID</sub> | Bulk capacitor for PMID        |     | 30  |     | μF |

| C <sub>BAT</sub>  | Bulk capacitor for VBAT        |     | 20  |     | μF |

| C <sub>VCC</sub>  | Bulk capacitor for VCC         |     | 1   |     | μF |

| L                 | Inductance                     | 1   | 2.2 | 3.3 | μH |

| T <sub>A</sub>    | Operating ambient temperature  | -40 | C   | 85  | °C |

| TJ                | Operating junction temperature | -40 |     | 125 | °C |

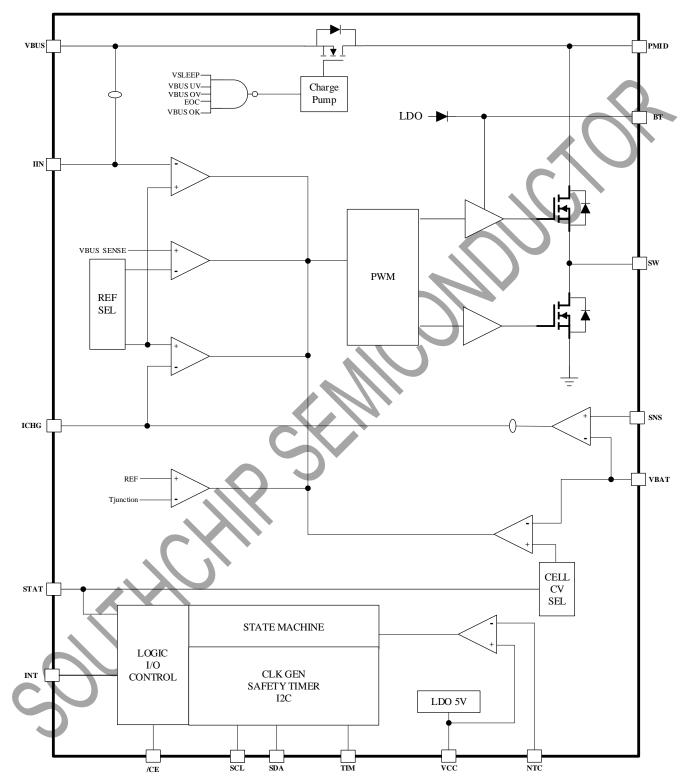

# 8 Function Block Diagram

# 9 Electrical Characteristics

$T_{J}\text{=}~25~^{\circ}\text{C}~$  and  $V_{\text{BUS}}$  = 12V, unless otherwise noted.

| PARAMETER                              | 2                                             | TEST CONDITIONS                                                                                                                                                    | MIN | TYP  | MAX          | UNIT       |

|----------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|--------------|------------|

| SUPPLY VOI                             | LTAGE                                         |                                                                                                                                                                    |     |      |              |            |

| V <sub>BUS</sub>                       | Operating input VBUS voltage                  |                                                                                                                                                                    | 4   |      | 14           | V          |

|                                        |                                               | Rising edge, for 1 cell                                                                                                                                            |     | 4.7  |              | V          |

| V <sub>BUS_OK</sub>                    | VBUS voltage to start charge                  | Rising edge, for 2 cell                                                                                                                                            |     | 9.4  |              | V          |

|                                        | VBUS under-voltage lockout                    | Rising edge                                                                                                                                                        |     | 3.6  | 3.9          | V          |

| V <sub>UVLO</sub>                      | threshold                                     | Hysteresis                                                                                                                                                         |     | 200  | $\checkmark$ | mV         |

|                                        |                                               | Falling edge                                                                                                                                                       |     | 80   |              | mV         |

| V <sub>SLEEP</sub>                     | $V_{\text{BUS}}$ - $V_{\text{BAT}}$ threshold | Hysteresis                                                                                                                                                         |     | 120  |              | mV         |

|                                        |                                               | $V_{BUS} = 12V, V_{BAT} = 8V, No$<br>Switching, /CE=0,<br>Reg 0x01 bit[4](EN_CHG)=0                                                                                |     | 0.29 | 0.54         | mA         |

| I <sub>Q_VBUS</sub>                    | V <sub>BUS</sub> supply current               | $V_{BUS} = 12V, V_{BAT} = 8V, No$<br>Switching, /CE=0,<br>Reg 0x01 bit[4](EN_CHG)=1<br>Reg 0x03 bit[3:0](I_{CHG})=0000                                             |     | 1.15 | 1.93         | mA         |

|                                        |                                               | $V_{BUS}$ =12V, $V_{BAT}$ = 8V, No switching,<br>/CE=0<br>Reg 0x01 bit[4](EN_CHG)=0                                                                                |     | 12   | 19.9         | μ <b>A</b> |

| I <sub>Q_VBAT</sub> V <sub>BAT</sub> : | V <sub>BAT</sub> supply current               | V <sub>BUS</sub> = V <sub>PMID</sub> =12V, V <sub>BAT</sub> = 8V, No<br>switching, /CE=0<br>Reg 0x01 bit[4](EN_CHG)=1<br>Reg 0x03 bit[3:0](I <sub>CHG</sub> )=0000 |     | 29   | 39.9         | μ <b>A</b> |

|                                        |                                               | $V_{BUS} = V_{PMID} = 12V, V_{BAT} = 8.4V, after EOC$                                                                                                              |     | 13   | 22.6         | μ <b>A</b> |

|                                        |                                               | V <sub>BUS</sub> = open, V <sub>BAT</sub> = 8V, /CE=0                                                                                                              |     | 7    | 12           | μ <b>A</b> |

| I <sub>SD_VBAT</sub>                   | Shutdown current into $V_{\text{BAT}}$ pin    | $V_{BUS}$ = open, $V_{BAT}$ = 8V ,<br>/CE=OPEN                                                                                                                     |     | 5    | 10.6         | μ <b>A</b> |

|                                        |                                               | $V_{\text{BUS}} = 12V, V_{\text{BAT}} = 8V ,$<br>/CE=OPEN                                                                                                          |     | 13   | 17.7         | μ <b>A</b> |

| POWER STA                              | GE                                            |                                                                                                                                                                    |     |      |              | •          |

| R <sub>DSON_Q1</sub>                   | Reverse blocking MOSFET on resistance         | V <sub>cc</sub> =5V                                                                                                                                                |     | 26   | 35           | mΩ         |

| R <sub>DSON_Q2</sub>                   | High side switching MOSFET on resistance      | V <sub>cc</sub> =5V                                                                                                                                                |     | 25   | 32           | mΩ         |

| R <sub>DSON_Q3</sub>                   | Low side switching MOSFET<br>on resistance    | V <sub>cc</sub> =5V                                                                                                                                                |     | 30   | 40           | mΩ         |

|                                        |                                               | Reg 0x04 bit[4:3]=00, fsw=400KHz                                                                                                                                   |     | 400  |              | KHz        |

|                                        |                                               | Reg 0x04 bit[4:3]=01, fsw=600KHz                                                                                                                                   |     | 600  |              | KHz        |

| f <sub>sw</sub>                        | Switching frequency                           | Reg 0x04 bit[4:3]=10, fsw=800KHz                                                                                                                                   |     | 800  |              | KHz        |

|                                        |                                               | Reg 0x04 bit[4:3]=11, fsw=1000KHz                                                                                                                                  |     | 1000 |              | KHz        |

SOUTHCHIP SOUTHCHIP SEMICONDUCTOR

| $t_{\text{MIN}_{OFF}}$ | Minimum off time                   |                                                                             |       | 160                   |       | ns |

|------------------------|------------------------------------|-----------------------------------------------------------------------------|-------|-----------------------|-------|----|

| VCC                    |                                    |                                                                             |       |                       |       |    |

| M                      | V <sub>cc</sub> LDO output voltage | $V_{BUS}$ = 12V, $I_{VCC}$ = 1~70mA                                         | 5     | 5.15                  | 5.3   | V  |

| V <sub>vcc</sub>       |                                    | V <sub>BUS</sub> = 5V                                                       | 4.9   | 4.99                  | 5     | V  |

| I <sub>vcc</sub>       | V <sub>cc</sub> current limiter    | $V_{BUS}$ = 12V, $V_{CC}$ = 3.8V                                            | 50    |                       |       | mA |

| CHARGER M              | MANAGEMENT                         |                                                                             |       |                       |       |    |

|                        |                                    | Reg 0x03 bit[3:0]=1010,I <sub>CHG</sub> =2A                                 |       |                       |       |    |

|                        |                                    | $R_{ICHG} = 5 \text{ k}\Omega, V_{BUS} = 5V, V_{BAT} = 4V$                  | 1.9   | 2                     | 2.1   | A  |

|                        |                                    | Reg 0x03 bit[3:0]=0101,I <sub>CHG</sub> =1A                                 | 0.05  |                       | 1.05  |    |

| I <sub>CHG</sub>       | Constant charging current          | $R_{ICHG}$ = 5 k $\Omega$ , $V_{BUS}$ =5V, $V_{BAT}$ =4V                    | 0.95  | 1                     | 1.05  | A  |

| CHG                    | accuracy                           | Reg 0x03 bit[3:0]=1010,I <sub>CHG</sub> =2A                                 |       |                       | 0.4   |    |

|                        |                                    | $R_{ICHG} = 5 \text{ k}\Omega, V_{BUS} = 12 \text{V}, V_{BAT} = 8 \text{V}$ | 1.9   | 2                     | 2.1   | A  |

|                        |                                    | Reg 0x03 bit[3:0]=0101,I <sub>CHG</sub> ≠1A                                 | 0.05  | 1                     | 1.05  | _  |

|                        |                                    | $R_{ICHG} = 5 \text{ k}\Omega, V_{BUS} = 12 \text{V}, V_{BAT} = 8 \text{V}$ | 0.95  | 1                     | 1.05  | A  |

|                        |                                    | Reg 0x06 bit[1:0]=00                                                        |       | 0.2* I <sub>CHG</sub> |       | Α  |

|                        | Constant charging current in       | Reg 0x06 bit[1:0]=01                                                        |       | 0.3* I <sub>CHG</sub> |       | А  |

| I <sub>CHG_JEITA</sub> | NTC cool state                     | Reg 0x06 bit[1:0]=10                                                        |       | 0.4* I <sub>CHG</sub> |       | A  |

|                        |                                    | Reg 0x06 bit[1:0]=11                                                        |       | 0.5* I <sub>CHG</sub> |       | А  |

|                        |                                    | Reg 0x05 bit[1:0]=00, V <sub>BUS</sub> =5V                                  | 150   | 200                   | 250   | mA |

| 1                      | Trickle charge current             | Reg 0x05 bit[1:0]=01, V <sub>BUS</sub> =5V                                  | 250   | 300                   | 350   | mA |

| TRICKLE                |                                    | Reg 0x05 bit[1:0]=10, V <sub>BUS</sub> =5V                                  | 350   | 400                   | 450   | mA |

|                        |                                    | Reg 0x05 bit[1:0]=11, V <sub>BUS</sub> =5V                                  | 450   | 500                   | 550   | mA |

|                        |                                    | Reg 0x05 bit[3:2]=00, V <sub>BUS</sub> =5V                                  | 45    | 100                   | 135   | mA |

|                        |                                    | Reg 0x05 bit[3:2]=01, V <sub>BUS</sub> =5V                                  | 140   | 200                   | 245   | mA |

| ITERM                  | Termination current                | Reg 0x05 bit[3:2]=10, V <sub>BUS</sub> =5V                                  | 230   | 300                   | 345   | mA |

|                        |                                    | Reg 0x05 bit[3:2]=11, V <sub>BUS</sub> =5V                                  | 330   | 400                   | 445   | mA |

|                        |                                    | Reg 0x02 bit[2:0]=001                                                       |       |                       |       |    |

|                        | V torget voltage                   | Reg 0x02 bit[3]=0, V <sub>BUS</sub> =5V                                     | 4.179 | .179 4.2              | 4.221 | V  |

| V <sub>BAT_TRGT</sub>  | V <sub>BAT</sub> target voltage    | Reg 0x02 bit[2:0]=011                                                       |       |                       |       |    |

|                        |                                    | Reg 0x02 bit[3]=0, V <sub>BUS</sub> =5V                                     | 4.279 | 4.3                   | 4.322 | V  |

|                               |                                                                    |                                          | 1     |      |       |    |

|-------------------------------|--------------------------------------------------------------------|------------------------------------------|-------|------|-------|----|

|                               |                                                                    | Reg 0x02 bit[2:0]=100                    | 4.328 | 4.35 | 4.372 | v  |

|                               |                                                                    | Reg 0x02 bit[3]=0, V <sub>BUS</sub> =5V  | 4.320 | 4.55 | 4.572 | v  |

|                               |                                                                    | Reg 0x02 bit[2:0]=101                    |       |      |       |    |

|                               |                                                                    | Reg 0x02 bit[3]=0, V <sub>BUS</sub> =5V  | 4.378 | 4.4  | 4.422 | V  |

|                               |                                                                    | Reg 0x02 bit[2:0]=001                    |       |      |       |    |

|                               |                                                                    | Reg 0x02 bit[3]=1, V <sub>BUS</sub> =12V | 8.358 | 8.4  | 8.442 | V  |

|                               |                                                                    | Reg 0x02 bit[2:0]=011                    | 0 557 | 9.6  | 0.642 | v  |

|                               |                                                                    | Reg 0x02 bit[3]=1, V <sub>BUS</sub> =12V | 8.557 | 8.6  | 8.643 | v  |

|                               |                                                                    | Reg 0x02 bit[2:0]=100                    | 0.057 |      |       |    |

|                               |                                                                    | Reg 0x02 bit[3]=1, V <sub>BUS</sub> =12V | 8.657 | 8.7  | 8.744 | V  |

|                               |                                                                    | Reg 0x02 bit[2:0]=101                    | 8.756 | 8.8  | 8.844 | V  |

|                               |                                                                    | Reg 0x02 bit[3]=1, V <sub>BUS</sub> =12V | 0.750 | 0.0  | 0.044 | v  |

|                               | Termination voltage over V <sub>BAT</sub> target in NTC warm state | Reg 0x06 bit[3:2]=00                     | 45    | 50   | 55    | mV |

| M                             |                                                                    | Reg 0x06 bit[3:2]=01                     | 90    | 100  | 110   | mV |

| V <sub>BATTRGT_JEITA</sub>    |                                                                    | Reg 0x06 bit[3:2]=10                     | 138   | 150  | 162   | mV |

|                               |                                                                    | Reg 0x06 bit[3:2]=11                     | 186   | 200  | 214   | mV |

| $V_{\text{BAT}\_\text{TERM}}$ | Termination threshold over V <sub>BAT</sub> target                 | Rising edge                              | 96.5  | 98   | 99.5  | %  |

|                               | Recharge threshold below V <sub>BAT_REG</sub>                      | Reg 0x02 bit[4]=0                        | 50    | 100  | 150   | mV |

| VBAT_RECH                     |                                                                    | Reg 0x02 bit[4]=1                        | 100   | 200  | 300   | mV |

|                               | Trickle charge threshold for 1                                     | Rising edge                              | 2.9   | 3    | 3.1   | V  |

|                               | celł                                                               | Hysteresis                               |       | 200  |       | mV |

| V <sub>TRK_CH</sub>           | Trickle charge threshold for 2                                     | Rising edge                              | 5.86  | 6    | 6.13  | V  |

| $\sim$                        | cell                                                               | Hysteresis                               |       | 400  |       | mV |

| $\sim$                        |                                                                    | Reg 0x04 bit[2:0]=010                    | 4.41  | 4.5  | 4.56  | V  |

| 3                             |                                                                    | Reg 0x04 bit[2:0]=011                    | 4.5   | 4.6  | 4.66  | V  |

| VINREG                        | Input voltage regulation                                           | Reg 0x04 bit[2:0]=100                    | 4.6   | 4.7  | 4.76  | V  |

|                               |                                                                    | Reg 0x04 bit[2:0]=011                    | 4.7   | 4.8  | 4.86  | V  |

|                               |                                                        | Reg 0x04 bit[2:0]=100                                                                                | 7.94  | 8.1  | 8.23         | V  |

|-------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------|------|--------------|----|

|                               |                                                        | Reg 0x04 bit[2:0]=111                                                                                | 10.5  | 10.8 | 10.99        | V  |

| I <sub>STAT</sub>             | Source current at STAT pin                             | STAT pin short to GND                                                                                |       | 4    |              | mA |

| $t_{\text{term\_dly}}$        | Termination delay time                                 |                                                                                                      |       | 4    |              | S  |

| $t_{\text{rech}\_\text{dly}}$ | Recharge delay time                                    |                                                                                                      |       | 5    |              | ms |

|                               | Obarra Cafatutiman                                     | Trickle charge safety timer,<br>$C_{TIM}$ =100nF, Reg 0x05 bit[7:6] = 01                             |       | 0.5  | $\langle \ $ | h  |

| t <sub>safety_timer</sub>     | Charge Safety timer                                    | CC/CV charge safety timer, C <sub>TIM</sub><br>=100nF, Reg 0x05 bit[5:4] = 01                        |       | 6    | )            | h  |

| PROTECTION                    |                                                        | I<br>                                                                                                |       |      |              |    |

|                               |                                                        | Reg 0x03 bit[6:4] = 011<br>$V_{BUS}$ =5V, $V_{BAT}$ =4V, I <sub>LIM_IN</sub> =1350mA                 | 1.25  | 1.35 | 1.5          | A  |

| I <sub>lim_in</sub>           | Input current limit                                    | Reg 0x03 bit[6:4] = 100<br>V <sub>BUS</sub> =5V,V <sub>BAT</sub> =4V,1 <sub>LIM_IN</sub> = 2000mA    | 1.86  | 2    | 2.1          | A  |

|                               |                                                        | Reg 0x03 bit[6:4] = 011<br>V <sub>BUS</sub> =12V,V <sub>BAT</sub> =8V, I <sub>LIM_IN</sub> =1350mA   | 1.25  | 1.35 | 1.5          | A  |

|                               |                                                        | Reg 0x03 bit[6:4] = 100<br>V <sub>BUS</sub> =12V, V <sub>BAT</sub> =8V, I <sub>LIM_IN</sub> = 2000mA | 1.86  | 2    | 2.1          | A  |

| I <sub>LIM_PK</sub>           | Internal peak current limit                            |                                                                                                      |       | 6.5  |              | A  |

| M                             | V <sub>BAT</sub> over voltage protection               | Rising edge, over V <sub>BAT</sub> target                                                            | 103.2 | 104  | 106.6        | %  |

| V <sub>BAT_OVP</sub>          |                                                        | Hysteresis, over V <sub>BAT</sub> target                                                             |       | 2    |              | %  |

| IBATOVP_DSG                   | V <sub>BAT</sub> over voltage discharge current        |                                                                                                      |       | 5    |              | mA |

|                               |                                                        | Rising edge                                                                                          | 13.65 | 14   | 14.35        | V  |

| V <sub>BUS_OVP</sub>          | Input over voltage protection                          | Hysteresis                                                                                           |       | 0.5  |              | V  |

| $T_{BUS\_OVP\_deglitch}$      | V <sub>BUS</sub> over voltage protection deglitch time |                                                                                                      |       | 100  |              | ns |

| T <sub>BATOVP_deglitch</sub>  | V <sub>BAT</sub> over voltage protection deglitch time |                                                                                                      |       | 40   |              | μs |

| 5                             |                                                        | Falling edge (1cell)                                                                                 | 1.9   | 2    | 2.1          | v  |

| V <sub>BAT_SC</sub>           | V <sub>BAT</sub> short circuit protection threshold    | Falling edge (2cell)                                                                                 | 3.8   | 4    | 4.2          | V  |

|                               |                                                        | Hysteresis                                                                                           |       | 200  |              | mV |

| I <sub>BAT_SC</sub>           | Regulation current for short circuit protection        |                                                                                                      |       | 150  |              | mA |

| V <sub>COLD</sub>     |                                                                |                                                      |      |      |      |    |

|-----------------------|----------------------------------------------------------------|------------------------------------------------------|------|------|------|----|

| VCOLD                 | NTC cold temp threshold,                                       | Rising                                               | 72.7 | 73.5 | 74.3 | %  |

|                       | as percentage of VCC                                           | Hysteresis (Falling)                                 |      | 1.3  |      | %  |

|                       | NTC cool temp threshold,                                       | Rising                                               | 64.6 | 65.4 | 66.2 | %  |

| V <sub>COOL</sub>     | as percentage of VCC                                           | Hysteresis (Falling)                                 |      | 1.3  |      | %  |

|                       | NTC warm temp threshold, as                                    | Falling                                              | 43.7 | 44.5 | 45.3 | %  |

| Vwarm                 | percentage of VCC                                              | Hysteresis (Rising)                                  |      | 1.3  |      | %  |

| V                     | NTC hot temp threshold, as                                     | Falling                                              | 33.5 | 34.3 | 35.1 | %  |

| V <sub>HOT</sub>      | percentage of VCC                                              | Hysteresis (Rising)                                  |      | 1.3  |      | %  |

| VDISNTC               | NTC disable threshold, refer to $V_{\text{CC}} \text{voltage}$ | Falling                                              | 4.7  | 5    | 6    | %  |

| t <sub>NTC_dgl</sub>  | NTC status deglitch time                                       |                                                      |      | 60   |      | ms |

| LOGIC                 |                                                                |                                                      |      |      |      |    |

| V <sub>IL</sub>       | /CE input low voltage threshold                                |                                                      |      |      | 0.4  | V  |

| V <sub>IH</sub>       | /CE input high voltage threshold                               |                                                      | 1.2  |      |      | V  |

| SOFT START            |                                                                |                                                      |      |      |      |    |

| t <sub>D</sub>        | Input delay time                                               |                                                      |      | 5    |      | μs |

| t <sub>debounce</sub> | Input debounce time                                            | From $V_{\text{BUS}}$ power up to starting switching |      | 200  |      | ms |

| t <sub>ss</sub>       | Soft start time                                                |                                                      |      | 10   |      | ms |

| THERMAL REG           | ULATION and SHUTDOWN                                           |                                                      |      |      |      |    |

| T <sub>REG</sub>      | Thermal regulation temperature                                 |                                                      |      | 120  |      | °C |

| т                     | Thermal shutdown temperature                                   |                                                      |      | 160  |      | °C |

| T <sub>SD</sub> -     | Thermal shutdown hysteresis                                    |                                                      |      | 30   |      | °C |

## **10 Feature Description**

#### 10.1 UVLO and Shutdown mode

The SC8932A is in shutdown when its input voltage is lower than VUVLO threshold. After VBUS rises above the UVLO threshold, the IC exits shutdown mode.

## 10.2 Charger Enable

The /CE pin is pulled high by a  $1.5M\Omega$  resistor internally.

- When /CE is pulled low, charger is enabled;

- When /CE is pulled float or high, IC is disabled;

#### 10.3 Soft Start

When IC exits shutdown, there is a 200ms debounce time before the IC starts operation. After VBUS rises 200mV higher than VBAT, a 10ms soft start is initiated.

#### 10.4 Charge management

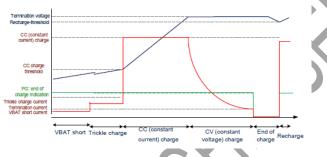

The SC8932A provides charge management functions for 1-2 cell Li-ion battery. The typical charge profile is shown in Figure 1.

Figure 1 Typical charge profile

Charger cycle starts when following conditions is satisfied:

- (1) VBUS\_OVP (14V)>VBUS >VBAT + 200mV;

- (2) /CE pin is pulled low;

- (3) No thermal fault(hot/cold) happens;

- (4) VBUS>VBUS OK;

## 10.4.1 Trickle Charge

When VBAT is lower than VTRK, the SC8932A charges the battery cells in trickle charge mode. In this mode, the charge current through Q3 is monitored and regulated at 300 mA(default), the Trickle Charge Current can be selected by register 0x05 bit[1:0].

#### 10.4.2 Constant Current(CC) Charge

When VBAT voltage is charged above VTRK, the SC8932A enters into constant charge (CC) mode. In this mode, the IC monitors 10 m $\Omega$  sense resistor current, and control the charging current decided by ICHG register 0x03 bit[3:0], default is 2000 mA.

#### 10.4.3 Constant Voltage(CV) Charge

The SC8932A operates in constant voltage (CV) mode after VBAT exceeds 98% of the termination voltage target VBAT\_TRGT. VBAT\_TRGT and cell number are controlled by register 0x02 bit [2:0] and 0x02 bit[3], default are 4.2V and 1 cell. In CV mode, the battery voltage is regulated at VBAT\_TRGT. The charge current automatically drops until the battery is fully charged.

#### 10.4.4 Charge Termination/End of Charge

When below conditions are valid, the SC8932A recognizes the battery cells are fully charged:

1) Termination voltage: the VBAT voltage is higher than 98% of VBAT\_TRGT

2) Termination current: the charge current is lower than 200mA. Termination current can be changed by register 0x05 bit[3:2], default is 200mA.

3) Above two conditions are met together and with 4s deglitch time

When battery is fully charged, the SC8932A outputs floating at STAT pin, so the LED connected at STAT pin is off, indicating the end of charge (EOC). EOC is disabled when IC is in VINREG, IIN limit or thermal regulation.

When charger enters into termination, the IC stops switching and turns off Q1.

#### 10.4.5 Recharge

After EOC, the SC8932A still monitors VBAT voltage. Once it detects the battery voltage falls 100mV lower than VBAT\_TRGT, it turns on charger and returns to CC mode again. Recharge Voltage can be changed by register 0x02 bit[4], default is 100mV.

#### **10.5 Charging Status Indication**

When the SC8932A charges the battery in trickle charge/CC charge/CV charge mode, the STAT pin outputs logic high, so the LED connected at STAT pin is turned on, indicating the charging is in process.

After the EOC conditions are met, the STAT pin outputs high

impedance, indicating the battery cells are fully charged.

If the battery voltage drops below the recharge threshold  $V_{\text{RECH}}$  the LED will be turned on again.

When fault happens, the STAT outputs high and low with 0.5Hz frequency.

#### Table 1 STAT STATUS

| STAT status | IC working status                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------------|

| HIGH        | Normal charging (TC/CC/CV/Recharge)                                                                   |

| Floating    | End of charging (EOC)                                                                                 |

| 0.5Hz       | Abnormal charging:<br>VBUSOVP/VBATOVP/Safety timer<br>triggered/NTC HOT/NTC COLD/Thermal<br>shut down |

## 10.6 Constant Charge Current Programming

The constant charge current can be programmed by ICHG register 0x03 bit[3:0], default is 2000 mA.

## 10.7 Input Current Limit

The SC8932A supports input current limit function. The input limit is selected by IBUS register 0x03 bit[6:4], default is 2000 mA.

## 10.8 Adaptive Input Current Limit

Besides the input current limit function, the SC8932A supports adaptive input current limit function (VINREG function) to prevent overloading the input adapter.

If the external adapter has smaller current capability than the current the IC draws, IC's VBUS voltage will be pulled down. Once the IC detects VBUS is pulled down, which indicates the adapter can't supply required current, the IC reduces the input current automatically. The input current is reduced to a value which can keep VBUS to be the programmed voltage, so to prevent the adapter from overloading further. This is called adaptive input current limit function or VINREG function.

If the adapter current capability is very low, the IC may enter into burst mode during this operation.

VINREG Voltage register is 0x04 bit[2:0], default is 4.5V.

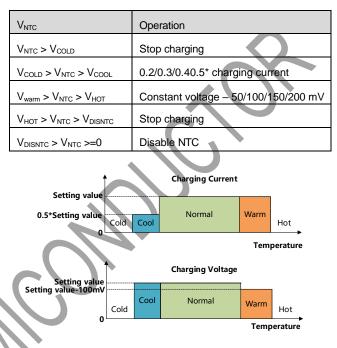

## 10.9 NTC

The SC8932A monitors the battery cells' temperature through NTC pin once VBUS is above ULVO threshold. It compares NTC pin voltage with VCC voltage. Once it detects the temperature is outside of the good range, the IC

transitions to shutdown mode. Below shows the NTC operation summary. NTC function can be also disabled through shorting the pin to ground.

| Table | 2 | NTC | op  | eration |

|-------|---|-----|-----|---------|

| Iabio | _ |     | ~ P | Juniori |

#### Figure 2 NTC Operation

SC8932A supports JEITA standard, IC monitors the voltage of NTC pin to check the temperature of battery. when IC detects the battery is in Cool State, it will decrease the constant charge current to be 0.5 ratio or 0.2 ratio. The ratio can be changed by register 0x06 bit[1:0], default is 0.5. Meanwhile, when IC detects the battery is in Warm State, it will decrease the constant voltage by 100mV, this voltage decreased value can also be programmed by register 0x06 bit[3:2], default is 100mV.

Battery Cool state and Warm state temperature can also be programmed by register 0x06 bit[7:6] and 0x06 bit[5:4], default are 15 degree and 45 degree.

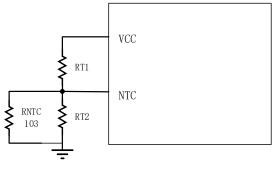

Figure 3 NTC Circuit

Use below equations to calculate the RT1/RT2 resistance when a 103AT NTC thermistor is used as shown in Figure 2.

$$R_{T2} = \frac{R_{COLD} \times R_{HOT} \times (\frac{1}{V_{COLD}} - \frac{1}{V_{HOT}})}{R_{HOT} \times (\frac{1}{V_{HOT}} - 1) - R_{COLD} \times (\frac{1}{V_{COLD}} - 1)}$$

$$R_{T1} = \frac{\frac{1}{V_{COLD}} - 1}{\frac{1}{R_{T2}} + \frac{1}{R_{COLD}}}$$

Where, RHOT is the NTC resistance at the hot temperature threshold, RCOLD is the resistance at the cold threshold.

For example, set 0 °C(cold) to 60 °C (hot) to be the charging range. So RCOLD = 28.71 K $\Omega$ , RHOT =2.99 K $\Omega$  (resistance of 103AT thermistor at 0°C and 60°C)

So the calculation results are:

RT1=5.19 KΩ, RT2=28.87 KΩ;

With above setting, the cool temperature and warm temperature are 10 °C and 45 °C.

#### 10.10 Input Over Voltage Protection

Besides under voltage protection, the SC8932A also supports input over voltage protection. Once the IC detects the input voltage is higher than 14V, it stops switching, turns off Q1 and STAT flashes at 0.5Hz. After the input voltage drops below VBUSOVP\_HYS, it resumes the normal operation. EOC detection is masked when VBUS OVP happens.

## **10.11 Over Current Protection**

SC8932A monitor the peak inductor current cycle by cycle, it will clamp the peak inductor current to be about 6.5A.

# 10.12VBAT Over Voltage Protection

The SC8932A monitors VBAT voltage during the operation. Once it detects the VBAT is higher than 104% of the target voltage, over voltage protection will be triggered, and the IC stops switching at once. After the VBAT voltage drops below 102% of the target, it resumes switching. Q1 status will not be affected by VBAT OVP.

## **10.13 VBAT Short Circuit Protection**

Once the IC detects the VBAT voltage drops below 2V, the VBAT short circuit protection is triggered. The IC regulates the short current to about 150mA.

After the short circuit fault is removed, the VBAT voltage is charged up. When VBAT voltage is higher than the short circuit threshold, the IC returns to normal operation.

If safety timer for trickle charged is triggered in VBAT short, IC will stop charging and turn off Q1. the IC will only restart the timer after VBUS toggles.

## 10.14 Safety Timer

Safety timer can be set by register 0x05 bit[7:6] and 0x05 bit[5:4]. 0x05 bit[7:6] is Trickle Charge Safety timer, default is 30 minutes, 0x05 bit[5:4] is CC or CV Safety timer, default is 6 hours.

Once safety timer is triggered, IC stops charging, and the STAT outputs 0.5Hz. IC resumes charging only when VBUS toggles.

When IC enters VINREG/IIN limit/Thermal regulation, the timer related safety timer time will double.

When the IC detects EOC condition, the IC clears the timer, and it doesn't restart the timer unless recharge phase starts or VBUS toggle happens.

If the charging cycle doesn't end when the timer expires, the IC will transition to shutdown mode. In this case, Charger stops, the IC will only restart the timer after VBUS toggles.

## 10.15 Thermal Regulation and Shutdown

In charging process, IC keeps monitoring junction temperature. When IC detects Tj >120°C, it enters into thermal regulation loop and charging current is decreased gradually. If Tj still exceeds 120°C, charging current can be decreased to 0;

Once the SC8932A detects the junction temperature rises above 160°C, it shuts down the whole chip. When the temperature falls below 130°C, the chip is enabled again.

## 10.16I2C and Interrupt

#### 10.16.1 I2C Interface

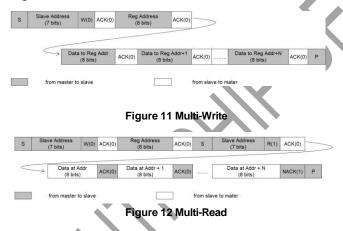

The IC features I2C interface, so the MCU or controller can control the IC flexibly. The 7-bit I2C address of the chip is 0x69 (8-bit address is 0XD2 for write command, 0XD3 for read command). The SDA and SCL pins are open drain and must be connected to the positive supply voltage via a current source or pull-up resistor. When the bus is free, both lines are HIGH. The I2C interface supports both standard mode (up to 100kbits) and fast mode (up to 400k bits with 5 k $\Omega$  pull up resistor at SCL pin and SDA pin respectively).

# SC8932A DATASHEET

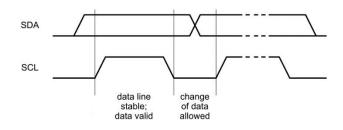

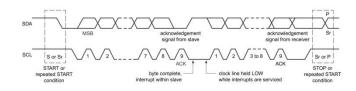

#### 10.16.2 Data Validity

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. One clock pulse is generated for each data bit transferred.

Figure 4 Bit transfer on the I2C bus

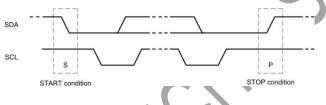

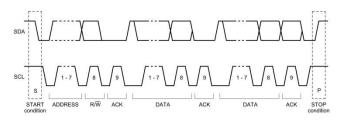

#### 10.16.3 START and STOP Conditions

All transactions begin with a START (S) and are terminated by a STOP (P). A HIGH to LOW transition on the SDA line while SCL is HIGH defines a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition.

START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition.

Figure 5 START and STOP conditions

#### 10.16.4 Byte Format

Every byte put on the SDA line must be eight bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte must be followed by an Acknowledge bit. Data is transferred with the Most Significant Bit (MSB) first. If a slave cannot receive or transmit another complete byte of data until it has performed some other function, for example servicing an internal interrupt, it can hold the clock line SCL LOW to force the master into a wait state. Data transfer then continues when the slave is ready for another byte of data and releases clock line SCL.

#### Figure 6 Data transfer on the I2C bus

# 10.16.5 Acknowledge (ACK) and Not Acknowledge (NACK)

The acknowledge takes place after every byte. The acknowledge bit allows the receiver to signal the transmitter that the byte was successfully received and another byte may be sent. During data is transferred, the master can either be the transmitter or the receiver. No matter what it is, the master generates all clock pulses, including the acknowledge ninth clock pulse.

The transmitter releases the SDA line during the acknowledge clock pulse so the receiver can pull the SDA line LOW and it remains stable LOW during the HIGH period of this clock pulse.

When SDA remains HIGH during this ninth clock pulse, this is defined as the Not Acknowledge signal. The master can then generate either a STOP condition to abort the transfer, or a repeated START condition to start a new transfer.

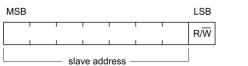

#### 10.16.6 The slave address and R/W bit

Data transfers follow the format shown in below. After the START condition (S), a slave address is sent. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W) — a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated START condition (Sr) and address another slave without first generating a STOP condition.

Figure 7 A complete data transfer

Figure 8 The first byte after the START procedure

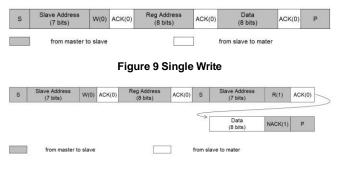

#### 10.16.7 Single Read and Write

| VBAT_OVP | Rising edge triggers 456us_pulse INT |

|----------|--------------------------------------|

| VBUS_OK  | Rising edge triggers 456us_pulse INT |

| EOC      | Rising edge triggers 456us_pulse INT |

| OTP      | Rising edge triggers 456us_pulse INT |

| TIME_OUT | Rising edge triggers 456us_pulse INT |

| COLD     | Rising edge triggers 456us_pulse INT |

| НОТ      | Rising edge triggers 456us_pulse INT |

The interrupt pulse at INT pin is as follow:

The INT signal can be masked when the corresponding control bit is set in register 0x0A. When an INT condition is masked, this means that the INT pin will not send a low pulse when the corresponding condition occurs but register status bit still works. Masking INTs is useful when writing software code to avoid unnecessary interruptions due to these events.

When an interrupt signal is asserted, the corresponding flag register (0x09) is kept unchanged until the host reads the state registers. The flag register bit is read and clear type.

#### Figure 10 Single Read

If the register address is not defined, the charger IC send back NACK and go back to the idle state.

#### 10.16.8 Multi-Read and Multi-Write

The IC supports multi-read and multi-write for continuous registers.

#### 10.16.9 Interrupt

Whensystemregister2(0x08)VBUSOVP/VBATOVP/VBUS\_OK/EOC/OTP/TIME\_OUT/COLD/HOT is set to 1, the IC sends an interrupt pulse asbelow at INT pin to inform MCU. It is summarized as below:

| Table | 3 | Interrupt | operation |

|-------|---|-----------|-----------|

| TUNIC | ~ | micinapi  | operation |

| Status Signal | Interrupt Triggering Mechanism       |

|---------------|--------------------------------------|

| VBUS_OVP      | Rising edge triggers 456us_pulse INT |

## **11** Application Information

#### 11.1 Input and Output Capacitor

The input current of the Buck converter is discontinuously and the input capacitor should be carefully selected. The ripple current through input capacitor can be calculated as:

$$IRMS = ICC \sqrt{\frac{VBAT}{VIN}(1 - \frac{VBAT}{VIN})}$$

where the ICC is battery charging current, the VIN is the input voltage(VBUS or PMID), VBAT is the battery voltage. Since MLCC ceramic capacitor has good high frequency filtering and low ESR, X5R or X7R capacitors are recommended for input capacitors. Three 10uF input capacitors in PMID is enough for most applications.

The output voltage ripple of output capacitor can be calculated as:

$$VRIPPLE = \frac{VBAT}{fsw \times L} (CESR + \frac{1}{8 \times fsw \times COUT})(1 - \frac{VBAT}{VIN})$$

Where the fsw is the switching frequency, CESR is the ESR of output capacitor. Also, X5R or X7R MLCC capacitors are recommended for output capacitors. Two 10uF output capacitors is enough for most applications.

MLCC capacitor of small package size normally has better high frequency filtering, so a 1  $\mu$ F MLCC of 0402 package size is highly recommended to added in parallel and put as close to VBUS and PMID pin as possible.

When selecting capacitors, the degrading effect of MLCC effective capacitance under DC bias must be considered. Ceramic capacitors can lose most capacitance at rated voltage. If the highest operating VBUS voltage is 12V,25V voltage rating capacitor is recommended. Check the effective capacitance at the operating voltage to make sure the voltage ripple can be maintained.

## 11.2 Inductor Selection

$1\mu$ H ~ 3.3  $\mu$ H inductor is recommended for loop stability.

The peak inductor current in charging mode can be calculated as

$$ILpeak = IBAT + \frac{VBAT \times (VBUS - VBAT)}{2 \times fsw \times L \times VBUS \times \eta}$$

where IBAT is the battery charging current at VBAT side.

$\eta$  is the power conversion efficiency. User can use 90% for calculation.

fsw is the switching frequency.

L is the inductor value.

When selecting inductor, the inductor saturation current must be higher than the peak inductor current with enough margin (20% margin is recommended). The rating current of the inductor must be higher than the battery current.

The inductor DC resistance value (DCR) affects the conduction loss of switching regulator, so low DCR inductor is recommended especially for high power application. The conductor loss of inductor can be calculated roughly as

$$PL_{DC} = IL^2 \times DCR$$

IL is the average value of inductor current, and it equals to IBAT.

Besides DC power loss, there are also inductor AC winding loss and inductor core loss, which are related to inductor peak current. Normally, higher peak current causes higher AC loss and core loss. The user shall consult with the inductor vendor to select the inductor which has small ESR at high frequency and small core loss.

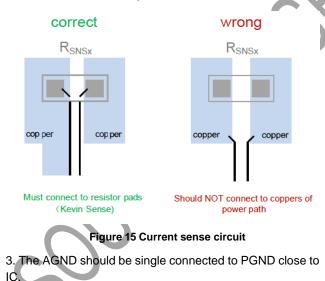

## 11.3 Current Sense Resistor

10 m $\Omega$  should be used to sense IBAT current. Resistor of 1% or higher accuracy and low temperature coefficient is recommended. The resistor power rating and temperature coefficient should be considered. The power dissipation can be roughly calculated as P=I<sup>2</sup>R, and I is the RMS current flowing through the resistor. The resistor power rating should be higher than the calculated value.

Normally the resistor value is varied if the temperature increased and the variation is decided by temperature coefficient. If high accuracy of current limit is required, select lower temperature coefficient resistor as much as possible.

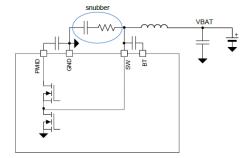

## 11.4 SW Snubber Circuit

To adjust MOSFET switching time and switching overshoot for EMI debugging, it is recommended to add RC snubber (0603 size) circuit at SW, as shown in Figure 14.

The RC snubber is helpful in absorbing the high frequency spike at SW node, so to improve EMC performance. User can leave RC components as NC at the beginning, and adjust the value to improve the EMC performance if necessary. Normally user can try 2.2 $\Omega$  and 1nF for the snubber. If EMC should be improved further, reduce the resistor value (like 1  $\Omega$  or even lower) and increase the capacitor value (like 2.2nF or even higher).

#### Figure 14 Snubber circuit

Meanwhile, the RC Snubber circuit will improve the IIN Limiter accuracy when the IC is used in high power application(15W for 1S, 24W for 2S) with a little bit efficiency reduce.

#### 11.5 Layout Guide

1. The capacitors connected at VBUS/PMID/VBAT/VCC pins should be placed near the IC, and their ground connection to the ground pins should be as short as possible.

2. The current sense resistor should be close to the IC. The current sense traces should be connected to the current sense resistor's pads in Kelvin sense way as below, and routed in parallel (differential routing), and the filter for current sense should be placed near the IC.

4. The SW RC snubber circuit should be very close to IC SW and PGND pin.

## 12 Register Map

7-bit address: 0x69; 8-bit address: 0XD2 for write command; 0XD3 for read command

#### Table 4 Register Map

| Addr | Register              | Туре | Default value | Bit 7                | Bit 6                    | Bit 5                 | Bit 4                 | Bit 3            | Bit 2           | Bit 1         | Bit 0            |

|------|-----------------------|------|---------------|----------------------|--------------------------|-----------------------|-----------------------|------------------|-----------------|---------------|------------------|

|      |                       |      | @POR          |                      |                          |                       |                       |                  |                 |               |                  |

| 01H  | SYSTEM CONTROL        | R/W  | 00111011      | Reserved             | Reserved                 | EN_JEITA              | EN_CHG                | EN_TIMER         | Reserved        | EN_AUTOTERM   | EN_TLOOP         |

| 02H  | CHARGE VOLTAGE        | R/W  | 0000001       | Reserved             | Reserved                 | Reserved              | RECHG_VOL             | CELL_NUM         |                 | VBAT_VOLTAGE  |                  |

| 03H  | CHARGE CURRENT        | R/W  | 01001010      | Reserved             | IBUS_SETTING ICHG_SETTIN |                       | TTING                 |                  |                 |               |                  |

| 04H  | CHARGE SETTING1       | R/W  | 00001010      | Reserved             | Reserved                 | DRV_SEL               | FREQ_                 | _SEL             | VINREG          |               |                  |

| 05H  | CHARGE SETTING2       | R/W  | 01010101      | TRK_                 | TIMER CC/CV_TIMER        |                       | TIMER                 | IT               | ERM TRK_CURRENT |               | RENT             |

| 06H  | JEITA CONTROL         | R/W  | 10010111      | JEITA                | _COOL JEITA_WARM         |                       | JEITA_WARM_VOL        |                  | JEITA_COOI      | L_CUR         |                  |

| 07H  | STATUS REGISTER1      | R    |               | CV_LOOP              | IBAT_LOOP                | IBUS_LOOP             | VINREG_LOOP           | T_LOOP           | OCP             | COOL          | WARM             |

| 08H  | STATUS REGISTER2      | R    |               | VBUS_OK              | VBUS_OVP                 | VBAT_OVP              | TIME_OUT              | EOC              | OTP             | COLD          | НОТ              |

| 09H  | STATUS<br>REGISTER2_F | R/C  |               | VBUS_OK_I<br>NT      | VBUS_OVP_<br>INT         | VBAT_OVP_INT          | TIME_OUT_INT          | EOC_INT          | OTP_INT         | COLD_INT      | HOT_INT          |

| 0AH  | INT_MASK              | R/W  | 00000000      | VBUS_OK_I<br>NT_MASK | VBUS_OVP_<br>INT_MASK    | VBAT_OVP_INT_<br>MASK | TIME_OUT_INT_<br>MASK | EOC_INT_MAS<br>K | OTP_INT_MASK    | COLD_INT_MASK | HOT_INT_M<br>ASK |

|     |      | 1           | Table                    | 5 0x01 System Control Register                       | 1     |

|-----|------|-------------|--------------------------|------------------------------------------------------|-------|

| Bit | Mode | Bit Name    | Default<br>value<br>@POR | Description                                          | Notes |

| 7-6 | R/W  | Reserved    | 00                       |                                                      |       |

| 5   | RW   | EN_JEITA    | 1                        | EN_JEITA<br>0: disable                               | 2     |

|     |      |             |                          | 1: enable (default)                                  |       |

| 4   | R/W  | EN_CHG      | 1                        | EN_CHG<br>0: disable 1: enable                       |       |

|     |      |             |                          | (default)                                            |       |

| 3   | R/W  | EN_TIMER:   | 1                        | EN_TIMER:<br>0: disable 1: enable<br>(default)       |       |

| 2   | R/W  | Reserved    | 0                        |                                                      |       |

| 1   | R/W  | EN_AUTOTERM | 1                        | EN_AUTOTERM:<br>0: No term<br>1: auto term (default) |       |

| 0   | R/W  | EN_TLOOP    | 1                        | EN_TLOOP:<br>0: disable 1: enable<br>(enable)        |       |

Table 5 0x01 System Control Register

\*

|     | I    |           | Table                    | e 6 0x02 Charge Voltage Register                                                                                                       |       |

|-----|------|-----------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|

| Bit | Mode | Bit Name  | Default<br>value<br>@POR | Description                                                                                                                            | Notes |

| 7-5 | R/W  | Reserved  | 00                       |                                                                                                                                        |       |

| 4   | R/W  | EN_JEITA  | 0                        | Recharge voltage selection<br>0: 100mV (default)<br>1: 200mV                                                                           | ~     |

| 3   | R/W  | CELL_NUM  | 0                        | CELL:<br>0: 1cell(default)<br>1: 2cell                                                                                                 |       |

| 2-0 | RW   | EN_TIMER: | 001                      | VCHG_1CELL[2:0]: 000:<br>4.1V<br>001: 4.2V (default)<br>010: 4.25V<br>011: 4.3V<br>100: 4.35V<br>101: 4.40V<br>110: 4.45V<br>111: 4.5V |       |

| 7   RW   Reserved   0   IBUS[2:0]   000:90mA     6-4   RW   IBUS   100   IBUS[2:0]   000:90mA     01:450mA   01:450mA   01:450mA   01:450mA     01:200mA (default)   10:200mA (default)   10:200mA     10:200mA   10:200mA   10:200mA     3-0   RW   ICHG   1010     ICHG[3:0]:   0000: disable charge   0001: 200mA     0010: 400mA   010: 400mA   010: 400mA     010: 100mA   011: 1000mA   011: 1000mA     010: 1000mA   010: 1000mA   011: 1000mA     010: 1000mA   010: 1000mA   011: 1000mA     010: 1000mA   010: 1600mA   010: 1800mA     010: 1800mA   101: 1200mA   011: 1400mA     0111: 1200mA   011: 1200mA   011: 1800mA     0111: 1200mA   1011: 1200mA   011: 1800mA | Notes | Table 7 0x03 Charge Current Register   Default Description   value @POR                                                                                                                                                                                            | Bit Name | Mode | Bit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-----|

| 6-4     R/W     IBUS     100     000:90mA<br>001:450mA<br>010:800mA<br>011:1350mA<br>100:2000mA (default)<br>101:2200mA       3-0     R/W     ICHG     1010     ICHG[3:0]:<br>0000: disable charge<br>0001: 200mA<br>0010: 400mA<br>0010: 400mA<br>0010: 400mA<br>0010: 1000mA<br>0011: 1000mA<br>0110: 1000mA<br>0110: 1000mA<br>0110: 1200mA<br>0110: 1200mA<br>0110: 1200mA<br>0110: 1200mA<br>0110: 1200mA<br>0110: 1200mA<br>0110: 1200mA                                                                                                                                                                                                                                       |       | 0                                                                                                                                                                                                                                                                  | Reserved | R/W  | 7   |

| 3-0 R/W ICHS 1010 0000: disable charge<br>0001: 200mA<br>0010: 400mA<br>0011: 600mA<br>0100: 800mA<br>0101: 1000mA<br>0110: 1200mA<br>0111: 1400mA<br>1010: 1600mA<br>1000: 1600mA<br>1000: 1600mA<br>1001: 1800mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       | 100 000:90mA<br>001:450mA<br>010:800mA<br>011:1350mA<br>100:2000mA (default)<br>101:2200mA<br>110:2800mA                                                                                                                                                           | IBUS     | RW   | 6-4 |

| 1100; 2400mA<br>1101; 2600mA<br>1110; 2800mA<br>1111; 3000mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | 1010<br>0000: disable charge<br>0001: 200mA<br>0010: 400mA<br>0011: 600mA<br>0100: 800mA<br>0101: 1000mA<br>0110: 1200mA<br>0111: 1400mA<br>1000: 1600mA<br>1001: 1800mA<br>1001: 2000mA (default)<br>1011: 2200mA<br>1100: 2400mA<br>1101: 2600mA<br>1110: 2800mA | ICHG     | R/W  | 3-0 |

|     |      | 1        | Table                    | 8 0x04 Charge Setting1 Register                                                                                                |

|-----|------|----------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Bit | Mode | Bit Name | Default<br>value<br>@POR | Description Notes                                                                                                              |

| 7-6 | R/W  | Reserved | 00                       |                                                                                                                                |

| 5   | R/W  | DRV_SET  | 0                        | DRV_SET:<br>0: fast (default)<br>1: slow                                                                                       |

| 4-3 | R/W  | FREQ     | 01                       | FREQ[1:0]:<br>00: 400Khz<br>01: 600Khz(default)<br>10: 800Khz<br>11: 1000KHz                                                   |

| 2-0 | R/W  | VINREG   | 010                      | VINREG[2:0]:<br>000: 4.3V<br>001: 4.4V<br>010: 4.5V(default)<br>011: 4.6V<br>100: 4.7V<br>101: 4.8V<br>110: 8.1V<br>111: 10.8V |

#### Table 9 0x05 Charge Setting2 Register

| Bit        | Mode  | Bit Name                           | Default<br>value | Description             | Notes |

|------------|-------|------------------------------------|------------------|-------------------------|-------|

|            |       |                                    | @POR             |                         |       |

| 7-6        | R/W   | TRK_TIMER                          | 01               | TRK_TIMER[1:0]:         |       |

|            |       |                                    |                  | 00:15MIN                |       |

|            |       |                                    | $\sim$           | 01:30MIN (default)      |       |

|            |       |                                    | $\sim$           | 10:45MIN                |       |

|            |       |                                    | $\sim$           | 11:60MIN                |       |

| <b>F</b> 4 | DAA   |                                    | 01               | CCCV_TIMER[1:0]:        |       |

| 5-4        | R/W   | CC/CV_TIMER                        | 01               | 00:4 Hr                 |       |

|            |       | $\mathbf{X} \mathbf{X} \mathbf{Y}$ |                  | 01:6 Hr (default)       |       |

|            |       |                                    |                  | 10:8 Hr                 |       |

|            |       |                                    |                  | 11:10 Hr                |       |

| 3-2        | R/W   | ITERM                              | 01               | ITERM[1:0]:             |       |

| 3-2        | -R/VV | ITERIM                             | 01               | 00:100mA                |       |

|            |       |                                    |                  | 01:200mA (default)      |       |

|            |       |                                    |                  | 10:300mA                |       |

|            |       |                                    |                  | 11:400mA                |       |

| 1-0        | R/W   | TRK_CUR                            | 00               | Trickle charge current: |       |

| 1-0        | 17/17 |                                    | 00               | 00: 200mA               |       |

|            |       |                                    |                  | 01: 300mA (default)     |       |

|            |       |                                    |                  | 10: 400mA               |       |

|            |       |                                    |                  | 11: 500mA               |       |

|     | Table 10 0x06 JEITA Control Register |                |                          |                                    |  |  |

|-----|--------------------------------------|----------------|--------------------------|------------------------------------|--|--|

| Bit | Mode                                 | Bit Name       | Default<br>value<br>@POR | Description Notes                  |  |  |

| 7-6 | R/W                                  | JEITA_COOL     | 10                       | JEITA_COOL_RISING_THRESHOLD[1:0]:  |  |  |

|     |                                      |                |                          | 00: 70.8%(5deg)                    |  |  |

|     |                                      |                |                          | 01: 68%(10deg)                     |  |  |

|     |                                      |                |                          | 10: 65.4%(15deg default)           |  |  |

|     |                                      |                |                          | 11: 62%(20deg)                     |  |  |

| 5-4 | R/W                                  | JEITA_WARM     | 01                       | JEITA_WARM_FALLING_THERSHOLD[1:0]: |  |  |

|     |                                      |                |                          | 00: 48.6%(40deg)                   |  |  |

|     |                                      |                |                          | 01: 44.5%(45deg default)           |  |  |

|     |                                      |                |                          | 10: 40.3%(50deg)                   |  |  |

|     |                                      |                |                          | 11: 37.8%(55deg)                   |  |  |

| 3-2 | R/W                                  | JEITA_WARM_VC  | 01                       | JEITA_WARM_VCHG[1:0]               |  |  |

| 02  |                                      | HG             | 01                       | 00: 50mV                           |  |  |

|     |                                      |                |                          | 01: 100mV(default)                 |  |  |

|     |                                      |                |                          | 10: 150mV<br>11: 200mV             |  |  |

|     |                                      |                |                          |                                    |  |  |

| 1-0 | R/W                                  | JEITA_COOL_ICH | 11                       | JEITA_COOL_ICHG[1:0]:              |  |  |

| 10  | 1.7.4.4                              | G              |                          | 00: 0.2*ICHG<br>01: 0.3*ICHG       |  |  |